## **Mercedes-Benz**

Company Standard

**MBN LV 148**

Date published: 2013-11 Supersedes: MBN LV 148 2012-03

Transition period: 0 months

Total no. of pages: 1 and 54 pages LV 148

Person in charge: Dr. Thomas Dörsam

E-mail: thomas.doersam@daimler.com

Plant: 059; Dept.: RD/EKS Phone: +49 151 586 099 50

Date of translation: 2013-12

# Electric and Electronic Components in Motor Vehicles - 48V On-Board Electrical System Requirements and Test Conditions

#### **Foreword**

This edition of this Standard is based on the document LV 148 which has been established by representatives of the automotive manufacturers AUDI AG, BMW AG, Daimler AG, Porsche AG and Volkswagen Aktiengesellschaft within Working Group AK 4.14, AG1 "14V On-Board Electrical System". If in individual cases modifications to individual test sections are required, such modifications shall be agreed separately between the departments responsible of the automotive manufacturer and the supplier. Within the framework of common development projects of the automotive manufacturers, test reports will be recognized provided that the tests have been performed by an independent institute accredited in accordance with DIN EN ISO/IEC 17025. Approval does not automatically follow from acceptance of the test reports. Other test reports may be recognized at the discretion of the customer.

The contents of LV 148 edition 2013-07 have been adopted unchanged into the set of standards of Mercedes-Benz. AK-LV documents cited in this MBN LV are usually adopted into the set of Mercedes-Benz standards as MBN LV documents with identical number.

#### Application note:

Application of the present version of this Standard is binding for new vehicle projects or components of this scope, for which no concept/basic specifications or component requirement specifications have been approved yet at the date of issue of this version.

The respective contract documents regulate the mandatory application of the present version of this Standard by the supplier.

#### General requirements

For safety requirements, homologation (in particular, exhaust emissions) and quality, the existing statutory requirements and laws shall be complied with. In addition, the relevant requirements of the Daimler Group apply.

All materials, procedures, processes, components, and systems shall conform to the current regulatory (governmental) requirements regarding regulated substances and recyclability.

## Changes

In comparison with edition MBN LV 148 2012-03, the following changes have been made: see page 2 of LV 148

**NOTE:** This translation is for information purposes only. The German version shall prevail above all others.

Copyright Daimler AG 2013

Issue: 2013-07

Electric and Electronic Components in Motor Vehicles

# **48-V Electric System**

# Requirements and Tests

#### **Preface**

This Supply Specification (LV) in the present issue was developed by representatives of automobile manufacturers Audi AG, BMW AG, Daimler AG, Porsche AG, and Volkswagen AG in working group (AK) 4.14, team (AG) 1, "14-V/48-V electric system and electric energy management."

This LV is stored as an MS Word file in the Audi AG Standards department.

No claim is made as to its completeness. The automobile manufacturers are entitled to require additional tests corresponding to the relevant state-of-the-art at any time.

Since the individual automobile manufacturers may make changes if necessary, only the automobile manufacturers' in-house standards that are based on this LV must be used.

Deviations from this LV are listed in the in-house standards on the cover sheet (in justified exceptional cases, deviations can be presented in italics in the text of the standard). If modifications of individual test sections are required in individual cases, these modifications must be agreed upon separately between the appropriate departments of the automobile manufacturer and of the supplier.

For general development projects of the automobile manufacturers, test reports will be accepted as long as the tests were performed by an independent institute that is accredited as per DIN EN ISO/IEC 17025. Acceptance of the test reports does not automatically result in a release. Other test reports may be accepted at the discretion of the purchaser.

# Dates of versions and revision record

| Date       | Section    | Brief description                                  | Responsible            |

|------------|------------|----------------------------------------------------|------------------------|

| 2011-08-29 | All        | New issue                                          | Mr. Radon              |

|            |            |                                                    | (on behalf of AK 4.14, |

|            | 117        | (Ex)                                               | ÀG 1)                  |

| 2013-07-18 | 2.1        | Revised/updated                                    | Mr. Radon              |

|            | 2.3.2      | Fig. 1 revised/updated                             | (on behalf of AK 4.14, |

| 1.K        | 2.3.2      | Storage protection voltage range updated           | AG 1)                  |

| - X        | 2.3.3      | Revised/updated                                    | 1.50                   |

| . 200      | 2.5        | Revised/updated                                    |                        |

|            | 3.1.1      | Revised/updated                                    |                        |

| - 11-      | 3.1.2      | Tab. 7 revised/updated                             | -///->                 |

|            | 3.1.2      | Fig. 3 added                                       |                        |

|            | 3.1.3      |                                                    |                        |

|            |            | Revised/updated                                    |                        |

|            | 3.2        | E48-01b Overvoltage in                             |                        |

|            | 3.2.1      | Revised/updated                                    |                        |

|            | 3.2.2      | Fig. 4 revised/updated                             |                        |

|            | 3.2.2      | Tab. 8 revised/updated                             |                        |

|            | 3.3        | E48-02 Transient overvoltage                       |                        |

|            | 3.3.1      | Revised/updated                                    | .47                    |

|            | 3.3.2      | Fig. 5 revised/updated                             | -17                    |

| 1          | 3.4.2      | Fig. 6 revised/updated                             |                        |

|            | 3.5.2      | Fig. 7 revised/updated                             | X                      |

|            | 3.5.2      | Tab. 11 corrected; V <sub>48maxmin,unlimited</sub> |                        |

|            | 3.6.2      | Tab. 12 revised/updated                            |                        |

|            | 3.6.3      | Tab. 13 revised/updated                            |                        |

| 17         | 3.6.3      | Fig. 8 revised/updated                             |                        |

| V          | 3.7.1.2    | Fig. 9 revised/updated                             |                        |

|            | 3.7.1.2    | Tab. 14 revised/updated                            |                        |

|            | 3.7.2.2    | Fig. 10 revised/updated                            |                        |

|            | 3.7.3.2    |                                                    |                        |

|            |            | Fig. 11 revised/updated                            |                        |

|            | 3.7.4      | Revised/updated                                    |                        |

|            | 3.8.2      | Fig. 12 revised/updated                            |                        |

|            | 3.9.2      | Tab. 18 revised/updated                            | 117                    |

|            | 3.9.2      | Fig. 13 revised/updated                            |                        |

|            | 3.10.2     | Fig. 14 revised/updated                            |                        |

| 1.K        | 3.11.2     | Tab. 20 revised/updated                            |                        |

| . X        | 3.11.2     | Fig. 16 revised/updated                            | 1/4                    |

| . 88>>     | 3.11.3.2   | Revised/updated                                    | ×>,                    |

| -(1)       | 3.12.2     | Revised/updated                                    |                        |

| 4          | 3.12.2     | Fig. 17 revised/updated                            |                        |

|            | 3.13.2     | Fig. 18 revised/updated                            | 5.1                    |

|            | 3.14.2     | Tab. 23 revised/updated                            |                        |

|            | 3.14.2     | Fig. 19 revised/updated                            |                        |

|            | 3.14.3     | Revised/updated                                    |                        |

|            | 3.16.2     | Tab. 25 "In B1" deleted                            |                        |

|            | 3.16.2     | Fig. 20 revised/updated                            |                        |

|            | 3.17.2     | Tab. 26 "In B1" deleted                            |                        |

|            |            | Fig. 21 revised/updated                            | 7-11-                  |

|            | 3.17.2     | , , , , , , ,                                      | .42                    |

|            | 3.18.2     | Tab. 27 "In B1" deleted                            | -1/2                   |

| V.         | 3.18.2     | Fig. 22 revised/updated                            | 1/21/                  |

|            | 3.19.1     | Fig. 23 revised/updated                            | X                      |

|            | 3.20.2     | Fig. 24 revised/updated                            |                        |

|            | 3.23 (new) | Test E48-21 added                                  |                        |

|            | 4          | Tab. 33 revised/updated                            |                        |

## Contents

|        |                                                                             | Page |

|--------|-----------------------------------------------------------------------------|------|

| 1      | Referenced standards                                                        |      |

| 2      | General part                                                                |      |

| 2.1    | Premises for components with BN48 connection                                |      |

| 2.2    | Requirements for components with BN48 connection                            | 8    |

| 2.3    | Terms and definitions                                                       |      |

| 2.4    | Sampling rates and measured value resolutions                               |      |

| 2.5    | Functional statuses                                                         | 13   |

| 2.6    | Operating modes                                                             | 14   |

| 2.7    | Parameter test                                                              | 14   |

| 2.8    | Continuous parameter monitoring with drift analysis                         | 14   |

| 2.9    | Physical analysis                                                           | 15   |

| 2.10   | Interface description                                                       | 15   |

| 3      | Electrical requirements and tests                                           | 16   |

| 3.1    | E48-01a Long-term overvoltage                                               | 16   |

| 3.2    | E48-01b Overvoltage in backfeeding components                               | 18   |

| 3.3    | E48-02 transient overvoltage                                                | 19   |

| 3.4    | E48-03 Transient process in the lower operating range with limited function |      |

| 3.5    | E48-04 Recuperation                                                         | 22   |

| 3.6    | E48-05 Superimposed AC voltage                                              | 23   |

| 3.7    | E48-06 Slow decrease and increase of the supply voltage                     |      |

| 3.8    | E-48-07 Slow decrease, quick increase of the supply voltage                 |      |

| 3.9    | E48-08 Reset behavior                                                       | 29   |

| 3.10   | E48-09 Short interruptions                                                  | 31   |

| 3.11   | E48-10 Start pulses                                                         | 33   |

| 3.12   | E48-11 Loss of ground BN48                                                  | 35   |

| 3.13   | E48-12 Ground offset                                                        | 38   |

| 3.14   | E48-13 Internal dielectric strength                                         | 39   |

| 3.15   | E48-14 Closed-circuit current                                               |      |

| 3.16   | E48-15 Operation in the range without functional limitation                 | 41   |

| 3.17   | E48-16 Operation in the upper range with functional limitation              |      |

| 3.18   | E48-17 Operation in the lower range with functional limitation              |      |

| 3.19   | E48-18 Overvoltage range                                                    |      |

| 3.20   | E48-19 Undervoltage range                                                   |      |

| 3.21   | E48-20 Fault current, part 1                                                |      |

| 3.22   | E48-20 Fault current, part 2                                                |      |

| 3.23   | E48-21 Short circuit in signal circuit and load circuit                     |      |

| Glossa | ry and abbreviations                                                        |      |

# List of figures

|                                                                                      | Page |

|--------------------------------------------------------------------------------------|------|

| Figure 1: Definitions of the static voltage ranges                                   | 9    |

| Figure 2: Component with two voltage supplies                                        | 11   |

| Figure 3: Test pulse E48-01a Long-term overvoltage                                   | 17   |

| Figure 4: Test pulse E48-01b Overvoltage in backfeeding components                   | 19   |

| Figure 5: Test pulse E48-02 Transient overvoltage                                    |      |

| Figure 6: Test pulse E48-03 Transient process in the lower range with limitations    | 21   |

| Figure 7: Test pulse E48-04 Recuperation                                             | 22   |

| Figure 8: Test pulse E48-05 Superimposed AC voltage                                  | 24   |

| Figure 9: Test pulse E48-06 Slow decrease and increase of the supply voltage         |      |

| Figure 10: Test pulse E48-06 for operation with storage, part 1                      | 26   |

| Figure 11: Test pulse E48-06 for operation with storage, part 2                      | 27   |

| Figure 12: Test pulse E48-07 Slow decrease and quick increase of the supply voltage  | 29   |

| Figure 13: Test pulse E48-08 Reset behavior                                          | 30   |

| Figure 14: Test pulses E48-09 Short interruptions                                    |      |

| Figure 15: Schematic circuit E48-09 Short interruptions                              | 32   |

| Figure 16: Test pulse E48-10 Start pulses                                            | 34   |

| Figure 17: Schematic circuit E48-11 BN48 loss of ground                              | 36   |

| Figure 18: Schematic circuit E48-12 Ground offset (V <sub>B48</sub> )                | 38   |

| Figure 19: Schematic circuit E48-13 Internal dielectric strength                     | 39   |

| Figure 20: Test pulse E48-15 Operation in the range without functional limitation    | 42   |

| Figure 21: Test pulse E48-16 Operation in the upper range with functional limitation | 44   |

| Figure 22: Test pulse E48-17 Operation in the lower range with functional limitation | 46   |

| Figure 23: Test pulse E48-18 Overvoltage range                                       | 48   |

| Figure 24: Test pulse E48-19 Undervoltage range                                      | 50   |

| Figure 25: Schematic circuit E48-20 Fault current, part 1                            | 51   |

| Figure 26: Schematic circuit E48-20 Fault current, part 2                            | 52   |

# List of tables

|                                                                                          | Page |

|------------------------------------------------------------------------------------------|------|

| Table 1: Referenced standards                                                            |      |

| Table 2: Abbreviations for voltages and currents                                         | 10   |

| Table 3: Abbreviations for temperatures                                                  |      |

| Table 4: Abbreviations for times                                                         |      |

| Table 5: Definition of standard tolerances                                               | 12   |

| Table 6: Definition of standard values                                                   | 12   |

| Table 7: Test parameters E48-01a Long-term overvoltage                                   | 16   |

| Table 8: Test parameters E48-01b Overvoltage in backfeeding components                   | 18   |

| Table 9: Test parameters E48-02 Transient overvoltage                                    | 20   |

| Table 10: Test parameters E48-03 Transient process in the lower range with limitations   | 21   |

| Table 11: Test parameters E48-04 Recuperation                                            | 22   |

| Table 12: Test parameters E48-05 Superimposed AC voltage                                 | 23   |

| Table 13: Test parameters E48-05 Superimposed AC voltage                                 |      |

| Table 14: Test parameters E48-06 Slow decrease and increase of the supply voltage        |      |

| Table 15: Test parameters E48-06 for operation with storage, part 1                      | 26   |

| Table 16: Test parameters E48-06 for operation with storage, part 2                      | 27   |

| Table 17: Test parameters E48-07 Slow decrease and quick increase of the supply voltage  | 28   |

| Table 18: Test parameters, E-48-08 Reset behavior                                        | 30   |

| Table 19: Test parameters E48-09 Short interruptions                                     |      |

| Table 20: Test parameters E48-10 Start pulses                                            |      |

| Table 21: Test parameters E48-11 BN48 loss of ground                                     |      |

| Table 22: Test parameters E48-10 Ground offset                                           |      |

| Table 23: Test parameters E48-13 Internal dielectric strength                            |      |

| Table 24: Test parameters E48-14 Closed-circuit current                                  | 40   |

| Table 25: Test parameters E48-15 Operation in the range without functional limitation    |      |

| Table 26: Test parameters E48-16 Operation in the upper range with functional limitation | 43   |

| Table 27: Test parameters E48-17 Operation in the lower range with functional limitation | 45   |

| Table 28: Test parameters E48-18 Overvoltage range                                       | 47   |

| Table 29: Test parameters E48-19 Undervoltage range                                      |      |

| Table 30: Test parameters E48-20 Fault current, part 1                                   |      |

| Table 31: Test parameters E48-20 Fault current, part 2                                   |      |

| Table 32: Test parameters E48-21 Short circuit in signal circuit and load circuit        |      |

| Table 33: Abbreviations                                                                  |      |

Page 6 LV 148 (2013-07)

## Scope

This document specifies requirements, test conditions, and tests for electric, electronic, and mechatronic components and systems for the use in motor vehicles.

Additional or deviating requirements, test conditions, and tests must be defined in the pertinent Component Performance Specifications.

The described tests are not used for component qualification or a qualification of the manufacturing process.

Part I – Electrical requirements<sup>1</sup>

## 1 Referenced standards

The following cited documents, see Table 1, are required for the use of this document. For dated references, only the referenced issue is valid. For undated references, the most recent issue of the referenced document (including all changes) is valid.

**Table 1: Referenced standards**

| DIN 72552-2          | Terminal Markings for Vehicles; Codes                                                                                                         |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| DIN 72552-4          | Terminal Markings for Vehicles; Summary                                                                                                       |

| DIN EN ISO/IEC 17025 | General Requirements for the Competence of Testing and Calibration Laboratories                                                               |

| ISO 6469-3           | Electrically Propelled Road Vehicles – Safety Specifications – Part 3: Protection of Persons Against Electric Shock                           |

| ECE-R100             | Uniform Provisions Concerning the Approval of Battery Electric Vehicles with Regard to Specific Requirements for Design and Functional Safety |

| LV 124               | Electric and Electronic Components in Motor Vehicles up to 3,5 t – General Component Requirements, Test Conditions, and Tests                 |

<sup>&</sup>lt;sup>1</sup>Part IIff.: See LV 124

## 2 General part

- LV 148 is an amendment to LV 124. It comprises the additional electrical tests of the 48 V electric system (BN48).

- LV 148 is valid for all components used in the 48-V electric system.

#### 2.1 Premises for components with BN48 connection

- For DC voltage ≤ 60 V, no electrical shock protection is required. This applies to DC voltages up to an electric system ripple of max. 10% RMS value.

For AC voltage V<sub>eff</sub> ≤ 30 V, no electrical shock protection is required (ISO 6469-3).

- A single fault in the wiring harness must not cause the BN48 to short circuit to the 12-V electric system (BN12)/24-V electric system (BN24) areas.

- There is a shared ground for BN12/BN24 and BN48, which are connected by spatially separated ground bolts/connections.

- All voltage and current specifications refer to the component (terminal voltage).

- Reversed polarity of the BN48 system is precluded by suitable solutions in the vehicle.

- An external start of BN48 is precluded by suitable solutions in the vehicle.

#### 2.2 Requirements for components with BN48 connection

- A single fault must not cause the BN48 to short circuit to the BN12/BN24.

- Components with parallel BN48 supply and BN12/BN24 supply, or connection between BN12 and BN48, require individual ground connections for both supply areas. These ground connections must be spatially separated from each other.

- The loss of ground connection of a BN48 component (T.31 and/or T.41) must not cause communication networks and electrical networks to malfunction or be destroyed.

- No component must enter the overvoltage range (e.g., due to a load dump or resonance step-up.

- Overcurrent tests must be specified in the Component Performance Specifications.

#### 2.3 Terms and definitions

## 2.3.1 Terminal designations

Terminal 40 is the positive line of the 48 V supply.

Terminal 41 is the ground cable of the 48 V supply.

The terminal designation is stipulated in DIN 72552-2 and DIN 72552-4.

## 2.3.2 Voltages and currents

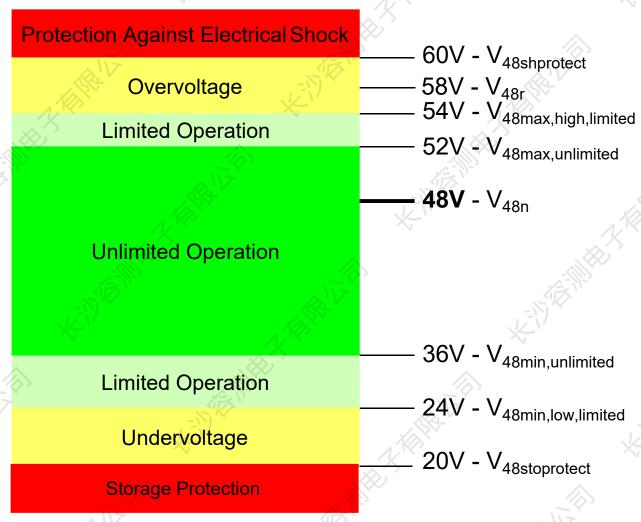

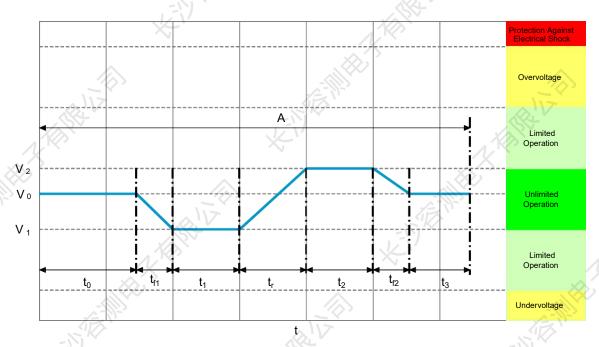

Figure 1: Definitions of the static voltage ranges

## **Electrical shock protection range**

In this range, DC voltages require electrical shock protection (see ECE-R 100).

#### Overvoltage range

The overvoltage range including all tolerances is between  $V_{48\text{max},\text{high},\text{limited}}$  and  $V_{48\text{r}}$ . In this range, the overvoltage protection must be active and voltages higher than  $V_{48\text{max},\text{high},\text{limited}}$  must be recorded by an event memory entry.

The range between  $V_{48r}$  and  $V_{48shprotect}$  includes the safety margin.

#### Upper operating voltage range with functional limitation

The range between  $V_{48max,unlimited}$  and  $V_{48max,high,limited}$  is used for calibrating the storage and the accommodation of backfeed energy.

## Operating voltage range without functional limitation

The range between  $V_{48min,unlimited}$  and  $V_{48max,unlimited}$  allows the components to be operated without functional limitation.

## Lower operating voltage range with functional limitation

Operation within the range from  $V_{48min,low,limited}$  to  $V_{48min,unlimited}$  is only temporarily permissible.

Remedial action to return to the operating voltage range without functional limitation is required.

## Undervoltage range

All voltages below  $V_{48\text{min,low,limited}}$  are defined as undervoltage and must be recorded as an event memory entry. The storage protection voltage is at  $V_{48\text{stoprotect}}$ .

## Storage protection voltage range

All voltages below V<sub>48stoprotect</sub>.

Table 2: Abbreviations for voltages and currents

| Abbreviation                    | Description                                                                                                                                                    | Value |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| V <sub>48shprotect</sub>        | Electrical shock protection voltage. Derived from the requirement to adhere to the limit value for electrical shock protection for DC voltages (see ECE-R 100) | 60 V  |

| $V_{48r}$                       | 2 V safety margin to the electrical shock protection voltage                                                                                                   | 58 V  |

| V <sub>48max,high,limited</sub> | Maximum voltage of the upper operating range with functional limitation                                                                                        | 54 V  |

| V <sub>48max,unlimited</sub>    | Maximum voltage of the operating range without functional limitation                                                                                           | 52 V  |

| V <sub>48n</sub>                | BN48 nominal voltage                                                                                                                                           | 48 V  |

| V <sub>48min,unlimited</sub>    | Minimum voltage of the operating range without functional limitation                                                                                           | 36 V  |

| V <sub>48min,low,limited</sub>  | Minimum voltage of the lower operating range with functional limitation                                                                                        | 24 V  |

| V <sub>48stoprotect</sub>       | Storage protection voltage                                                                                                                                     | 20 V  |

| V <sub>48pp</sub>               | Peak-to-peak voltage                                                                                                                                           | X     |

| V <sub>48rms</sub>              | RMS value of a voltage                                                                                                                                         |       |

| V <sub>48max</sub>              | Maximum voltage that may occur during a test                                                                                                                   |       |

| V <sub>48min</sub>              | Minimum voltage that may occur during a test                                                                                                                   |       |

| V <sub>48test</sub>             | BN48 test voltage                                                                                                                                              |       |

| V <sub>12test</sub>             | BN12 test voltage                                                                                                                                              |       |

| GND48                           | Device ground (T.41)                                                                                                                                           |       |

## 2.3.3 Test setup

The general conditions from DIN EN ISO/IEC 17025 apply.

Unless explicitly stated otherwise, the specified voltage curves refer to the terminal voltages of the device under test (DUT). They must be measured using the test setup and documented.

The specified voltage thresholds under  $V_{48 \text{shprotect}}$  must be adhered to on the component with an accuracy

of  $\pm 1\%$  (measured at the connector or at the control module terminal).

A tolerance margin of 0% to -1% applies to the V<sub>48shprotect</sub> threshold.

Before each test the event memory must be cleared.

After each test the event memory must be read and documented.

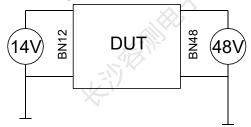

All BN48 components with an interface to the BN12 supply or with communication interfaces must additionally fulfill LV 124:

- BN12 must fulfill the requirements of LV 124. During the tests as per LV 124, the voltage is V<sub>48n</sub> unless specified otherwise in the individual tests of LV 124.

- During the tests of BN48, the BN12 voltage is 14,0 V unless specified otherwise in the individual tests.

It must be ensured in addition, and documented accordingly, that a random voltage or a random voltage curve within the defined limits on BN48 does not destroy the component on BN12 or cause a function failure. This also applies to destruction of the DUT due to the test pulse on the BN48 side.

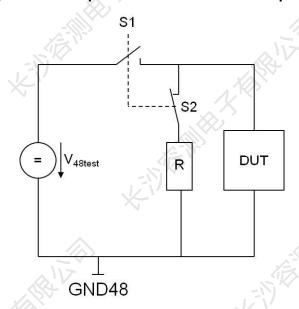

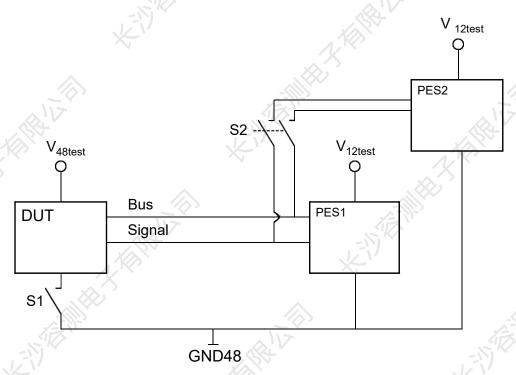

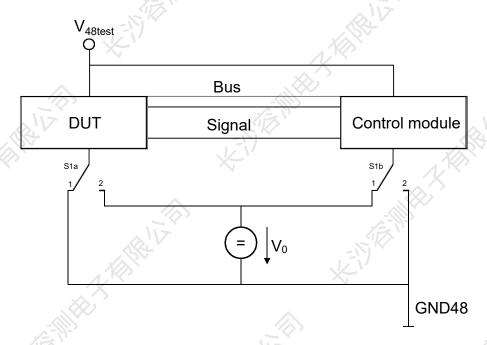

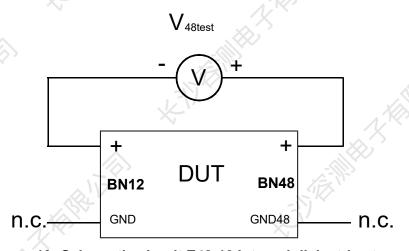

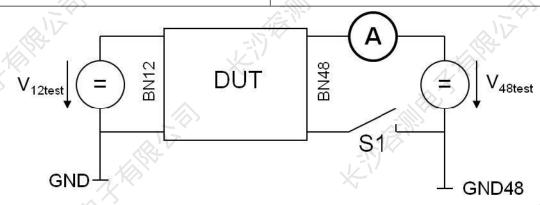

See Figure 2: Component with two voltage supplies.

Figure 2: Component with two voltage supplies

## 2.3.4 Temperatures

**Table 3: Abbreviations for temperatures**

| Abbreviation      | Description                   | Unit - |

|-------------------|-------------------------------|--------|

| T <sub>min</sub>  | Minimum operating temperature | °C - I |

| T <sub>RT</sub>   | Room temperature              | ı°C    |

| T <sub>max</sub>  | Maximum operating temperature | °C     |

| T <sub>test</sub> | Test temperature              | °C     |

#### 2.3.5 Times

**Table 4: Abbreviations for times**

| Abbreviation      | Description                         | Unit      |

|-------------------|-------------------------------------|-----------|

| t <sub>r</sub>    | Rise time, e.g., of a voltage curve | ms (A)    |

| t <sub>f</sub>    | Fall time, e.g., of a voltage curve | ms        |

| t <sub>test</sub> | Test duration                       | s, min, h |

All edge descriptions refer to the 10% or 90% voltage values.

## 2.3.6 Standard tolerances

Unless otherwise indicated, the tolerances as per Table 5: Definition of standard tolerances apply. Tolerances of envelopes must always be considered unilaterally as, otherwise, the requirement is mitigated.

Tolerances refer to the required set value.

Table 5: Definition of standard tolerances

| Abbreviation     | Description       |     | Tolerance limits |

|------------------|-------------------|-----|------------------|

| f                | Frequencies       |     | ±1%              |

| T                | Temperatures      |     | ±2 °C            |

| H <sub>rel</sub> | Relative humidity | AIZ | ±5%              |

| t                | Times             |     | +5% to 0%        |

| V                | Voltages          | YK, | ±0,5%            |

| I                | Currents          |     | ±2%              |

## 2.3.7 Standard values

Unless otherwise indicated, the standard values as per Table 6: Definition of standard values apply.

**Table 6: Definition of standard values**

| Abbreviation      | Description                             | A THE | Value                                    |

|-------------------|-----------------------------------------|-------|------------------------------------------|

| T <sub>RT</sub>   | Room temperature                        | -17   | 23 °C ±5 °C                              |

| H <sub>rel</sub>  | Relative humidity                       |       | 25% (+5% to 0%)<br>to<br>75% (-5% to 0%) |

| T <sub>test</sub> | Test temperature                        |       | T <sub>RT</sub>                          |

| Ri                | Internal resistance of the voltage soul | rce   | 10 mΩ ≤ $R_i$ ≤ 100 mΩ                   |

## 2.4 Sampling rates and measured value resolutions

The sampling rate and bandwidth of the measuring system must be adapted to the respective test. All measured values with all maximum values (peaks) must be recorded.

The resolution of the measured values must be adapted to the respective test. It must be ensured that occurring voltage peaks do not lead to an overflow or cannot be measured in the case of an insufficient resolution.

#### 2.5 Functional statuses

This section describes the functional status of the DUT during and after the test. The functional status of the DUT must be specified for each test. Both the exact functional requirements placed on the DUT in the operating statuses and additional requirements must be defined in the Component Performance Specification and documented.

The functional status A is the highest requirement placed on the component.

The data memory function must be ensured for the duration of storing in all functional statuses.

The integrity (not up-to-dateness) of the non-volatile memories must be ensured at any time.

The functional statuses are entered in the test descriptions in the pertinent figures, using the letters A to D.

#### 2.5.1 Functional status A

The components are operational without limitation and provide their specified function.

#### 2.5.2 Functional status B

The components continue to be operational without limitation. The components provide a function within the deviations permissible for functional status B. The components must automatically provide their specified function on return to functional status A.

#### 2.5.3 Functional status C

The components continue to be operational, must not assume undefined statuses and, in particular, must not cause any other components to malfunction. The components may reduce their electrical power for reasons of self-protection. The components must automatically provide their specified function on return to functional status A or B.

## 2.5.4 Functional status D

The components continue to be operational, and they must not assume undefined statuses. The components may reduce their electrical power to zero. At the end of the exposure, the DUT must return to functional status A by means of a reset (e.g., change of ignition status, new start of the vehicle).

#### 2.6 Operating modes

The electric, electronic, and mechatronic components and systems are operated in different operating modes during service life, which must be simulated correspondingly during the tests. Details concerning the operating modes, operating loads (e.g. triggering, original sensors, original actuators or replacement circuitry) and the required preconditions must be agreed upon between contractor and purchaser and must be documented.

The operating mode required during the test must represent the most demanding requirement for the component. Deviations must be defined in the Component Performance Specification.

## 2.6.1 Operating mode I – DUT not electrically connected

## 2.6.1.1 Operating mode l.a

The DUT is without current, connectors and wiring harness are not connected.

## 2.6.1.2 Operating mode l.b

The DUT is without current, but connectors and wiring harness are connected.

#### 2.6.2 Operating mode II – DUT electrically connected

Components that are electrical source and sink must be tested in both operating modes.

## 2.6.2.1 Operating mode II.a

The DUT must be operated without operating load.

#### 2.6.2.2 Operating mode II.b

The DUT must be operated with minimal operating load.

The DUT must be operated in a way that minimal self-heating occurs (e.g., by reducing a continuous output power or by infrequent activation of external loads).

#### 2.6.2.3 Operating mode II.c

The DUT must be operated with maximum operating load.

The DUT must be operated in a way that maximum self-heating occurs (e.g., by means of a realistic maximization of a continuous output performance or frequent activation of external loads).

#### 2.7 Parameter test

All parameters that must be separately monitored during the test must be defined in the Component Performance Specification for the pertinent tests with value ranges.

#### 2.8 Continuous parameter monitoring with drift analysis

The key parameters to be monitored must be recorded during the whole test.

For components with event memory, the event memory must be monitored continuously and the entries must be documented.

The data resulting from the continuous parameter monitoring must be examined for trends and drifting to detect irregularities, aging, or malfunctions of the component.

## 2.9 Physical analysis

For the physical analysis, the DUT must be opened and visually inspected for damage.

Additional analyses (e.g. X-ray examinations and metallographic examinations of the assembly and joining technology) must be coordinated between purchaser and contractor.

## 2.10 Interface description

All interfaces must be described completely in their statuses and electrical properties. This description serves as a basis for the evaluation of the test results and, thus, must be available in detail.

## 3 Electrical requirements and tests

Each DUT systematically goes through all tests.

After each individual test, the DUT is checked for external integrity and tested for unlimited functionality before the next test is performed. The test for unlimited functionality must be defined in the Component Performance Specification.

Damaged DUTs must be withdrawn from the test cycle and documented. If applicable, the test must be repeated with a new DUT, or the following test must be performed with a new DUT. The procedure must be agreed upon with the purchaser.

The test plan must be agreed upon with the purchaser.

The functional status specified in the test is the minimum requirement for this test.

The permissible event memory entries and the functional statuses of the component must be specified for each test.

## 3.1 E48-01a Long-term overvoltage

#### 3.1.1 Aim

The component's resistance to long-term overvoltage is tested.

## 3.1.2 Test

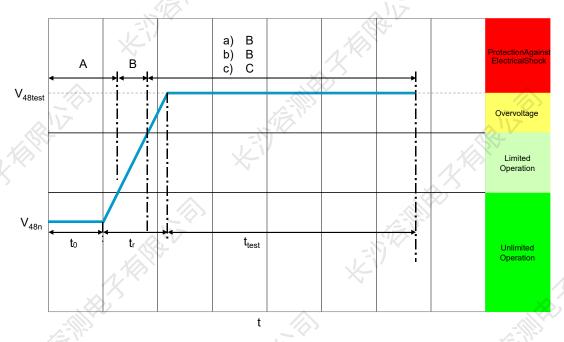

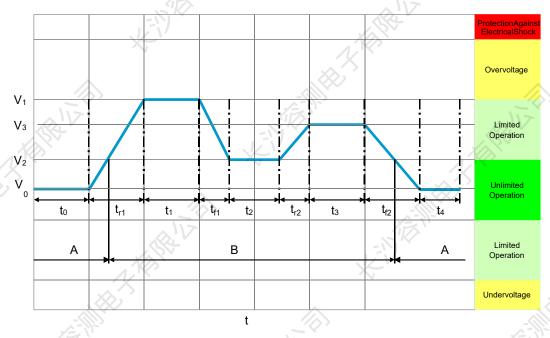

Table 7: Test parameters E48-01a Long-term overvoltage

| Operating mode II.a, II.b, and II.c |

|-------------------------------------|

| Functional status A assumed         |

| 0,1 s                               |

| 60 min                              |

| V <sub>48shprotect</sub>            |

| T <sub>max</sub> -20 °C             |

| 1 💢                                 |

| 6                                   |

|                                     |

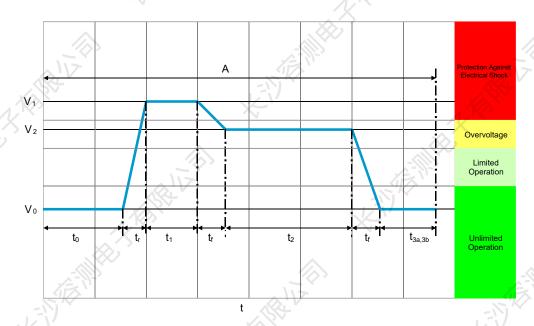

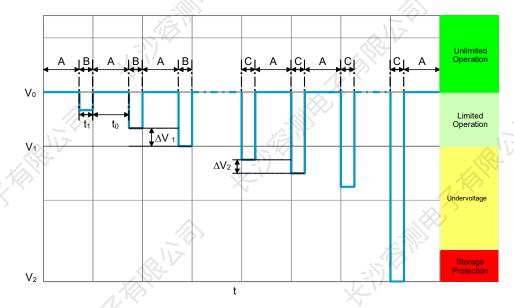

Figure 3: Test pulse E48-01a Long-term overvoltage

## 3.1.3 Requirement

The evaluation of the test results depends on the use of the component. A distinction is made between:

a) Components that are designed to handle high levels of electrical power (e.g., ohmic loads): Functional status B

b) Functions required for driving operation: Functional status B

c) For all other components: Functional status C

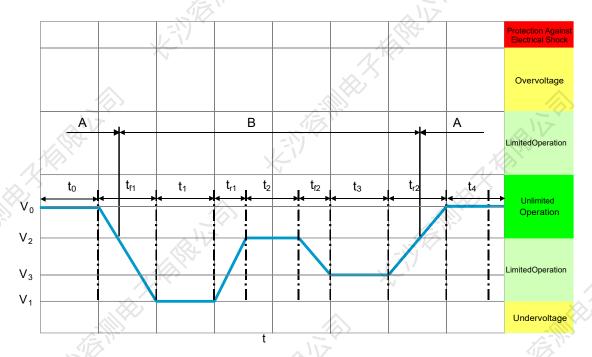

## 3.2 E48-01b Overvoltage in backfeeding components

#### 3.2.1 Aim

This test applies for all backfeeding components because they must have a voltage-limiting function to ensure protection against electrical shock. A scenario is simulated in which the component feeds power to the BN48 which cannot be accommodated by the electric system, therefore causing a voltage increase.

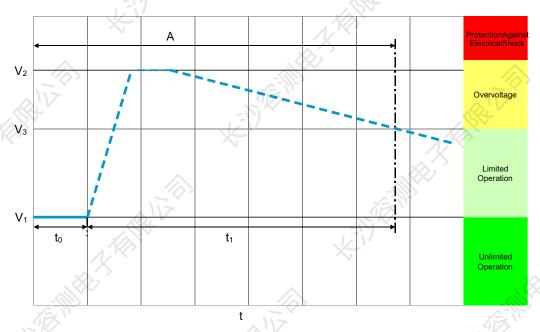

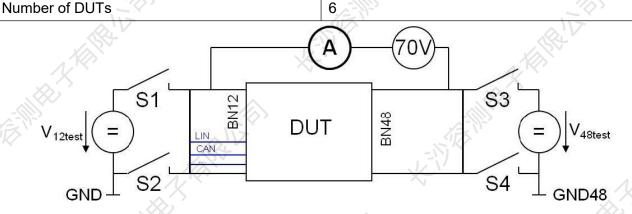

#### 3.2.2 Test

The DUT is connected to a powerful source.

During operating mode II.c with maximum backfeed, the source must be immediately separated from the component.

Table 8: Test parameters E48-01b Overvoltage in backfeeding components

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | ↑ I/Z                                      |

|----------------------------------------|--------------------------------------------|

| DUT operating mode                     | Operating mode II.c                        |

| T <sub>test</sub>                      | T <sub>RT</sub>                            |

| V <sub>1</sub>                         | V <sub>48max,unlimited</sub>               |

| V <sub>2</sub>                         | V <sub>48r</sub>                           |

| V <sub>3</sub>                         | V <sub>48max,high,limited</sub>            |

| to                                     | After reaching the maximum backfeed output |

| t <sub>1</sub>                         | After falling below V <sub>3</sub>         |

| Number of cycles                       | 3                                          |

| Number of DUTs                         | 6                                          |

|                                        |                                            |

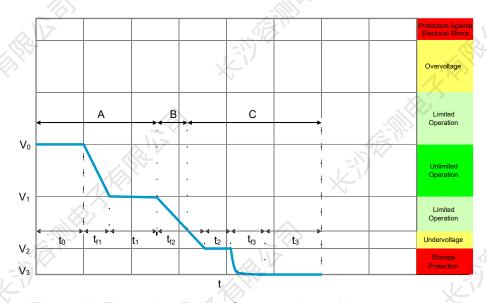

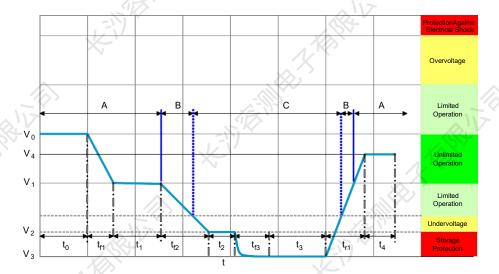

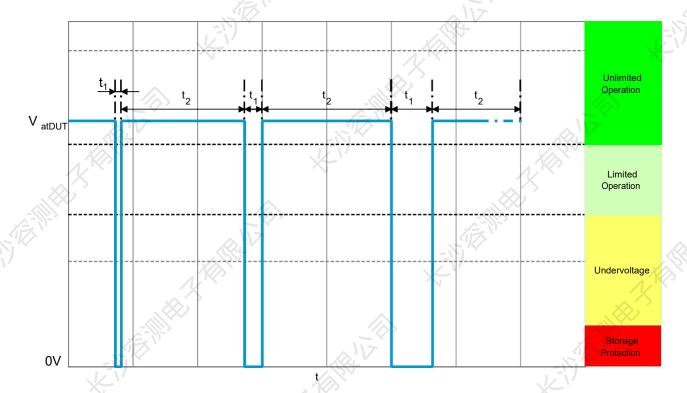

Figure 4: Test pulse E48-01b Overvoltage in backfeeding components

## 3.2.3 Requirements

Functional status A

The voltage on the component must be ≤V<sub>48r</sub> during the entire test.

## 3.3 E48-02 transient overvoltage

## 3.3.1 Aim

Transient overvoltages may occur in the BN48. These overvoltages are simulated by means of this test.

## 3.3.2 Test

Table 9: Test parameters E48-02 Transient overvoltage

| DUT operating mode | Operating mode II.c                                    |

|--------------------|--------------------------------------------------------|

| V <sub>0</sub>     | V <sub>48n</sub>                                       |

| V <sub>1</sub>     | 70 V                                                   |

| V <sub>2</sub>     | V <sub>48r</sub>                                       |

| t <sub>0</sub>     | 100 ms                                                 |

| t i                | 1 ms                                                   |

| t <sub>1</sub>     | 100 ms                                                 |

| t <sub>f</sub>     | 1 ms                                                   |

| t <sub>2</sub>     | 600 ms                                                 |

| t <sub>3a</sub>    | 2,5 s                                                  |

| t <sub>3b</sub>    | 9 s                                                    |

| Ri                 | $10 \text{ m}\Omega \leq R_i \leq 100 \text{ m}\Omega$ |

| Number of cycles   | 1. Short test: 3x with t <sub>3a</sub>                 |

|                    | 2. Long test: 1 000x with t <sub>3b</sub>              |

| 117                | Both tests are carried out in succession.              |

| Number of DUTs     | 6                                                      |

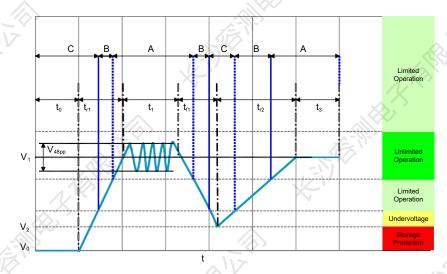

Figure 5: Test pulse E48-02 Transient overvoltage

## 3.3.3 Requirements

Functional status A

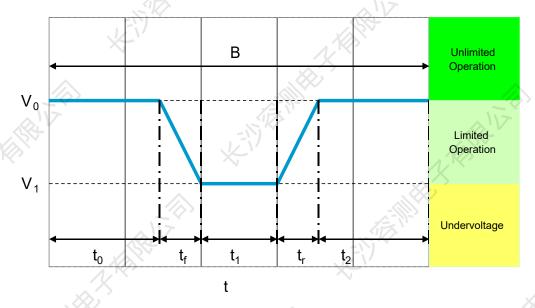

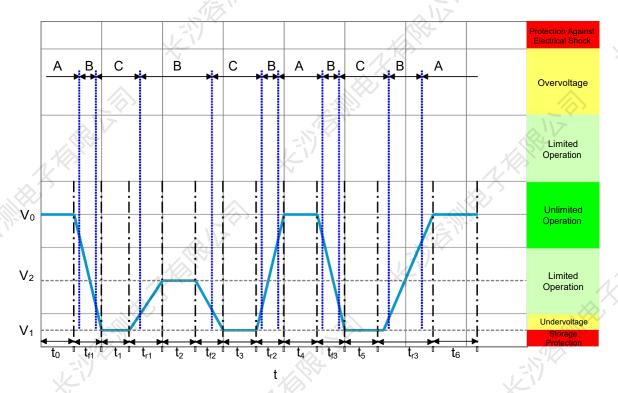

## 3.4 E48-03 Transient process in the lower operating range with limited function

## 3.4.1 Aim

Transient undervoltages in the electric system may occur due to switching on of loads. These undervoltages are simulated by means of this test.

## 3.4.2 Test

Table 10: Test parameters E48-03 Transient process in the lower range with limitations

| DUT operating mode | Operating mode II.c            |       |

|--------------------|--------------------------------|-------|

| V <sub>0</sub>     | V <sub>48min,unlimited</sub>   | E. T. |

| V <sub>1</sub>     | V <sub>48min,low,limited</sub> |       |

| to                 | 60 s                           | N.K.  |

| t <sub>f</sub>     | 1,8 ms                         |       |

| t <sub>1</sub>     | 500 ms                         |       |

| t <sub>r</sub>     | 1,8 ms                         |       |

| t <sub>2</sub>     | 500 ms                         | X.    |

| Number of cycles   | 1                              |       |

| Number of DUTs     | 6                              |       |

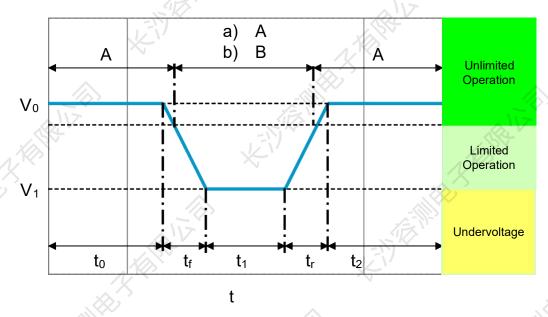

Figure 6: Test pulse E48-03 Transient process in the lower range with limitations

## 3.4.3 Requirement

Functional status B

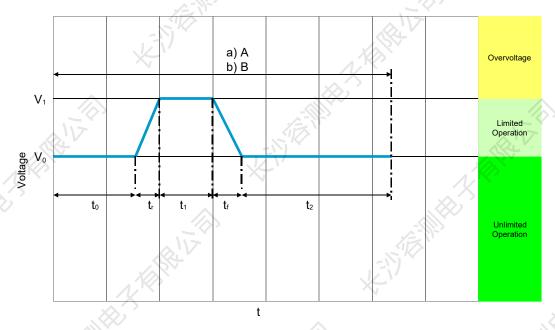

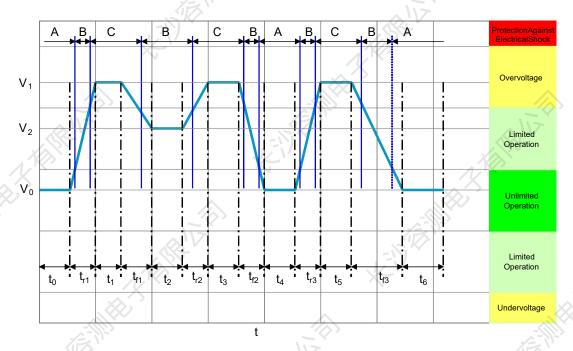

## 3.5 E48-04 Recuperation

## 3.5.1 Aim

This test simulates a longer phase of recuperation.

## 3.5.2 Test

Table 11: Test parameters E48-04 Recuperation

| DUT operating mode | Operating mode II.c             | XX    |

|--------------------|---------------------------------|-------|

| V <sub>0</sub>     | V <sub>48max,unlimited</sub>    |       |

| V <sub>1</sub>     | V <sub>48max,high,limited</sub> |       |

| $t_0$              | 60 s                            | X     |

| tr                 | 100 ms                          | . X × |

| t <sub>1</sub>     | 60 s                            |       |

| t <sub>f</sub>     | 100 ms                          | É.    |

| t <sub>2</sub>     | 60 s                            | -15   |

| Number of cycles   | 1                               | X,    |

| Number of DUTs     | 6                               |       |

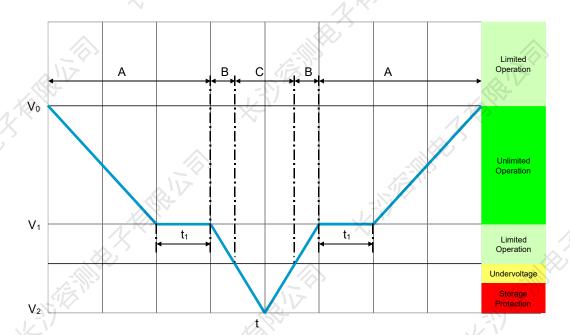

Figure 7: Test pulse E48-04 Recuperation

## 3.5.3 Requirements

The evaluation of the test results depends on the use of the component. A distinction is made between:

a) Components relevant for recuperation and driving operation:

Functional status A

b) For all other components:

Functional status B

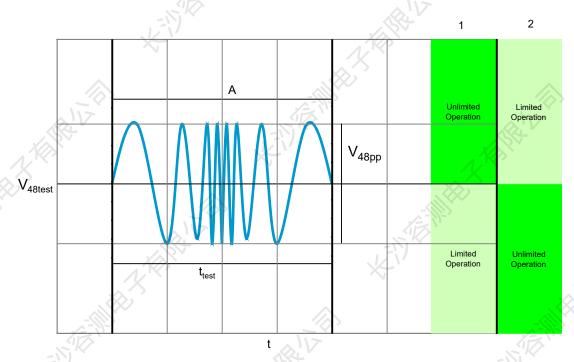

## 3.6 E48-05 Superimposed AC voltage

## 3.6.1 Aim

Voltages may be superimposed to the electric system. The superimposed AC voltage may be applied during the entire generator operation mode. This situation is simulated by means of this test.

## 3.6.2 Test part 1

Table 12: Test parameters E48-05 Superimposed AC voltage

| DUT operating mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Operating mode II.c                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Ri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $R_i = 60 \text{ m}\Omega$                      |

| V <sub>48test</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>48min,unlimited</sub>                    |

| t <sub>test</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30 min                                          |

| f -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F1: 15 Hz to 30 kHz                             |

| A CONTRACTOR OF THE PARTY OF TH | F2: 30 kHz to 200 kHz                           |

| Wobble period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2 min                                           |

| Wobble type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Triangle, logarithmic                           |

| $V_{48pp}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | For F1: 6 V (to be set before DUT is connected) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | For F2: 2 V (to be set before DUT is connected) |

| Number of DUTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                               |

## 3.6.3 Test part 2

Table 13: Test parameters E48-05 Superimposed AC voltage

| DUT operating mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Operating mode II.c                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Ri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $R_i = 60 \text{ m}\Omega$                      |